I was involved into that project for developing Standard Cell Libary for IDEC(IC Design Education Center).

Professor Kyung founded IDEC in 1994 and managed MPW(Multi-Project Wafer) for students can have the chance to design chips. However, there was significant limitation that they only possible to design very simple circuits as the foundry company did not provide Standard Cell Library for the confidential reasons.

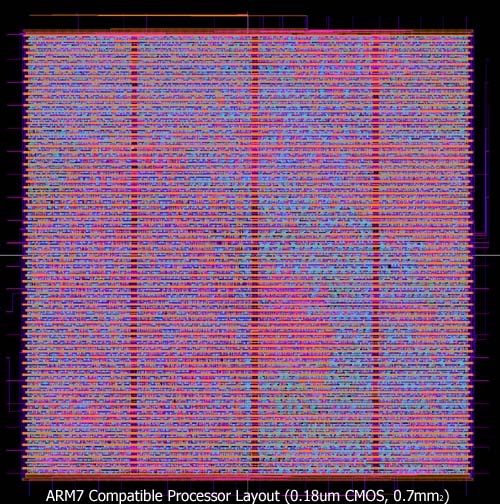

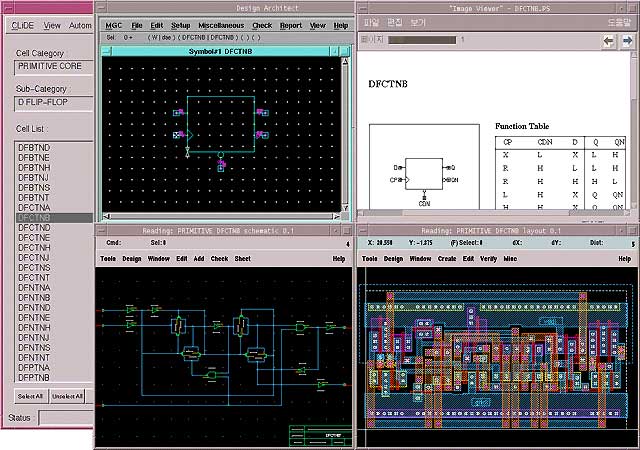

Standard Cell Library is a group of basic logic circuits including AND-gate, OR-gate and inverters that is ready-made to synthesis complex system chips. In order to synthesize a design, the schematic, function, timing characteristics and layouts are designed and registered to CAD softwares including Synopsys DesignCompiler, Cadence Verilog Simulators and P&R tools such as Astro.

For those reasons, IDEC had decided to develop the own Standard Cell Library. As there is very little information for library development at that time, however, there was too little progress for almost a year. Then I was involved as a troubleshooter and I reported the dramatic progress at the weekly project meeting every time.

One of the most serious problem is P&R(Place & Route). There were the functional issues and availablity issues due to the limited license. After several months, I all cleared the problem and wrote User’s Manual make CDs for distribution. The name of the library was named as IDEC-C631 which means CMOS 0.6um Triple Metal library.

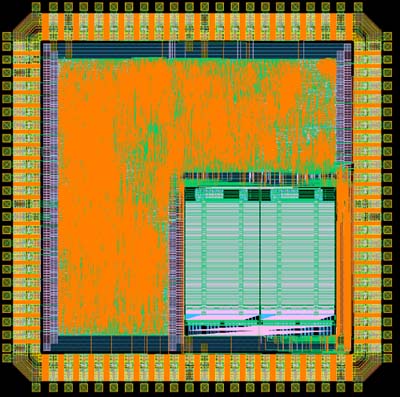

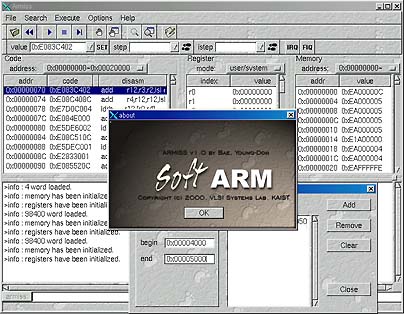

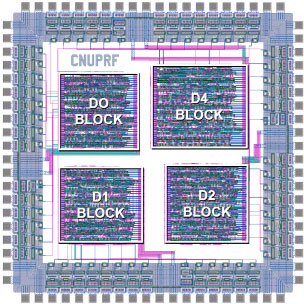

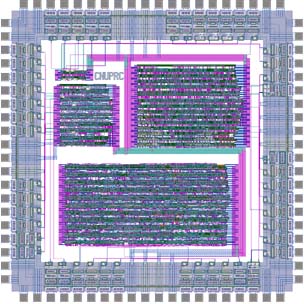

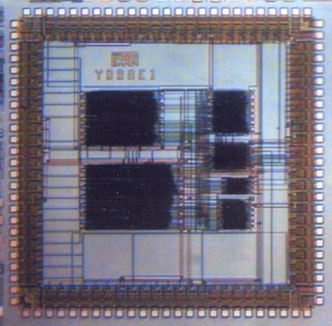

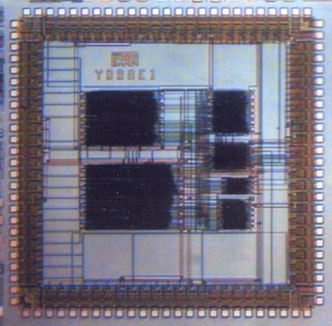

The test vehicle for validate the library was a microprocessor, MISC (Minimal Instruction Set Computer). Dr. Park wrote the verilog code and I synthesized it into the layout with IDEC-C631 library. If the one of schematic, layout, function and timing description for a single cell among the total 100 cells has a mistake, the chip would not operate. However, the results are very successful.

It is the first microprocessor that has my name on it.

MISC프로세서의 Die Photo

Young-Don Bae (www.donny.co.kr)