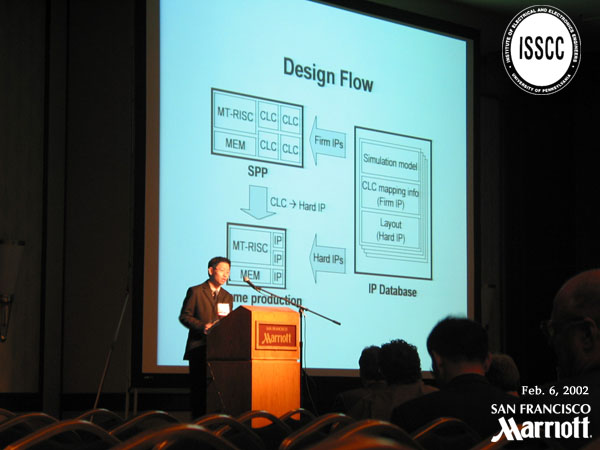

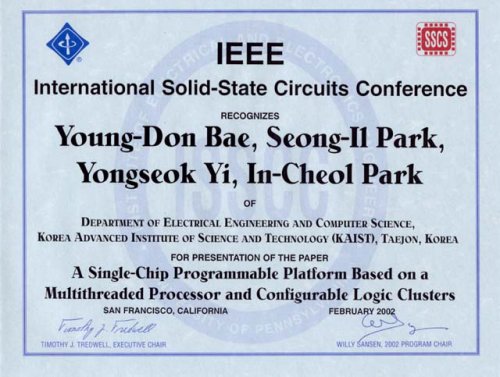

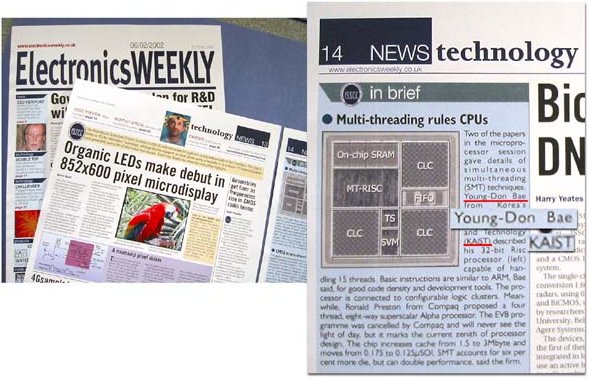

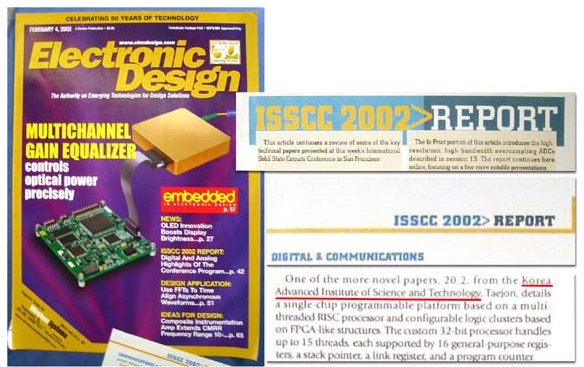

In the year 2002, I presented the paper about the multithreaded processor incorporating configurable logics at ISSCC (International Solid-State Circuit Conference).

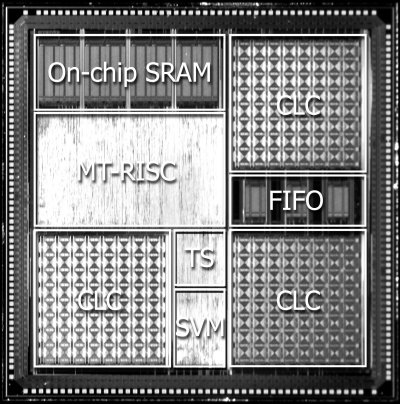

Until then multithreading was just one of the concepts in the papers or textbooks. I adapted the multithreading concept to ARM processor to enhance concurrent control for complex behavior for system chip and configurable logics for implement dedicated hardwares.

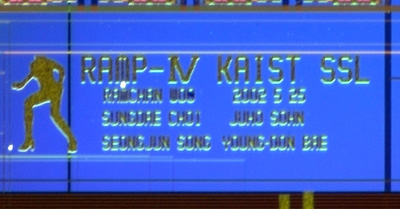

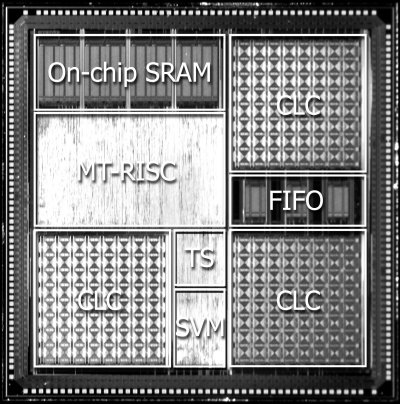

The block names as CLC (Configurable Logic Cluster) is a type of FPGA (Field Programmable Gate Array) for ASIC foundry. I designed the architecture for programmable logic including routings and look-up tables, drew the layout and ported it to P&R software by myself.

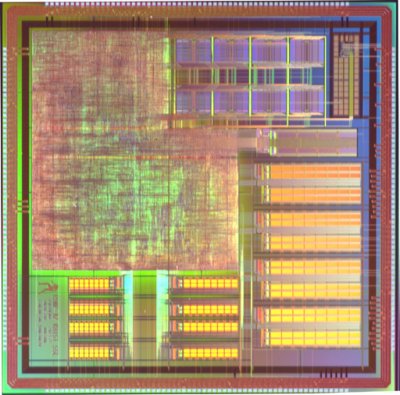

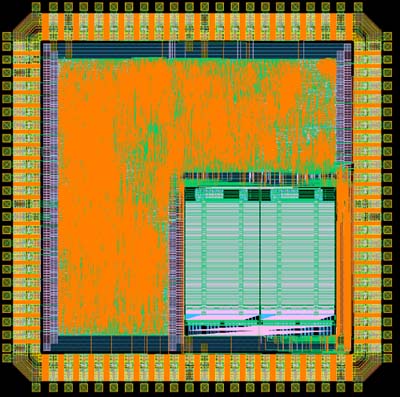

Die Photo of Single-Chip Programmable Platform

It was the great honor for me as it is the first paper presented in the microprocessor session in ISSCC for my mother country. It is very obvious how it is hard to present a paper for its microprocessor session if you have a look on the program book below as all the papers came from industry top companies including Compaq, Sun, IBM, Intel, Hewlett Packard.

The picture above was taken after the rehearsal at the day before the conference with the chairman, co-chairman and other speekers for the same session. The co-chairman was Simon Segars, Executive Vice President of ARM Ltd. As I was involved in the ARM compatible processor development project for years, I read his articles many times and my design is also based on ARM architecture. So it was very nice to see him and very challenging to rehearse in fromt of him.

simplecore1-1.pdf

simplecore1-1.pdf